Max Pin Tolerance Exceeds Calculated Pad Size

Printed From: PCB Libraries Forum

Category: Libraries

Forum Name: Altium

Forum Description:

URL: https://www.PCBLibraries.com/forum/forum_posts.asp?TID=3307

Printed Date: 15 May 2026 at 4:16am

Topic: Max Pin Tolerance Exceeds Calculated Pad Size

Posted By: Michael Ramonette

Subject: Max Pin Tolerance Exceeds Calculated Pad Size

Date Posted: 18 Aug 2023 at 10:19am

|

A nominal footprint that was

created with the parts calculator with a pin max width of 0.35 mm and a minimum width of 0.30. The concern I have is the pad is calculated at 0.32 mm and if we get a batch of parts that are created at the max tolerance the pin will overhang the pad on the b measurement. Is this correct or am I missing something? What do I tell my Engineers?

|

Replies:

Posted By: Tom H

Date Posted: 18 Aug 2023 at 12:21pm

|

What version of Footprint Expert are you using? What is the component family of the footprint you're creating? ------------- Stay connected - follow us! https://twitter.com/PCBLibraries" rel="nofollow - X - http://www.linkedin.com/company/pcb-libraries-inc-/" rel="nofollow - LinkedIn |

Posted By: Michael Ramonette

Date Posted: 18 Aug 2023 at 2:36pm

|

16 pin QFN with pad I had my librarian re-create it with a newer version of library expert with the same results.

MAX8556ETE+ |

Posted By: Tom H

Date Posted: 18 Aug 2023 at 2:55pm

|

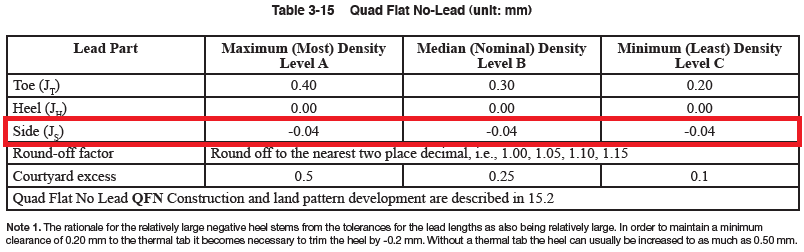

The Side solder joint goal for the "Flat No-Lead (Side)" is set to -0.04. If this is troubling you and your engineers then do this. Go to "Tools > Options > Terminals > Surface Mount > Flat No-Lead (Side) > Side goal" and change the value from -0.04 to -0.02 and your pad width will recalculate to 0.36 mm All the values in Footprint Expert are editable. If you don't like a value set forth in the IPC-7351B standard then change it. Here is the Flat No-Lead Table 3-15 in IPC-7351B (and an explanation of the negative solder joint goals:  ------------- Stay connected - follow us! https://twitter.com/PCBLibraries" rel="nofollow - X - http://www.linkedin.com/company/pcb-libraries-inc-/" rel="nofollow - LinkedIn |

Posted By: Michael Ramonette

Date Posted: 18 Aug 2023 at 4:28pm

|

Does this violate IPC-7351B or C? We have an IPC library and are contently questioned on parts created for one reason or another. If it does violate IPC suggestions I will be creating this as alternate part.

|

Posted By: Tom H

Date Posted: 18 Aug 2023 at 4:59pm

|

IPC-7351C was canceled and replaced with IPC-7352 which includes through-hole technology. IPC-7352 is NOT a Standard. It's a Generic Guideline for Land Pattern Design. There's no such thing as violating a Guideline. A Guideline is a suggestion or recommendation. You mentioned that the default side solder joint goal for a Flat No-Lead QFN is 0.03 mm smaller than the maximum terminal lead width. Tell your engineers that you're adjusting the "Guideline" by less than 1 mil because you're paranoid that the pad width is too small. The main reason why the Guideline suggests a -0.04 mm side goal is because of the 0.40 mm pin pitch QFN where the pad sides would be too close together and violate your minimum pad to pad spacing. Also, you can't run a trace between a 0.50 mm pin pitch QFN. So the maximum lead hanging over the pad slightly won't affect anything. ------------- Stay connected - follow us! https://twitter.com/PCBLibraries" rel="nofollow - X - http://www.linkedin.com/company/pcb-libraries-inc-/" rel="nofollow - LinkedIn |

Posted By: dramos

Date Posted: 21 Aug 2023 at 12:13pm

|

Dear Michael, Which values are you using for fabrication/assembly tolerances in this case? The default values? 0.00 mm? Regards. David

|

Posted By: Tom H

Date Posted: 21 Aug 2023 at 12:34pm

|

0.00 Fabrication & Assembly Tolerances are the new norm per IPC-7352. But all the negative solder joint goals are 0.00 too. There is an IPC-7352.opt file that updates all the options to do this. However, if you open the IPC-7352.opt file, don't forget to save it under a different name before you start editing it because it will be overwritten with a new installation. ------------- Stay connected - follow us! https://twitter.com/PCBLibraries" rel="nofollow - X - http://www.linkedin.com/company/pcb-libraries-inc-/" rel="nofollow - LinkedIn |